- /**************************************************

- module: LED_test

- author: wanganran

- description: The testbench for module LED_shining

- input:

- output:

- date: 2015.11.05

- **************************************************/

- `timescale 1ns / 100ps

- module LED_test;

- parameter CLK_PERIOD = 40; //CLK_PERIOD=40ns, Frequency=25MHz

- reg sys_clk;

- initial

- sys_clk = 1'b0;

- always

- sys_clk = #(CLK_PERIOD/2) ~sys_clk;

- reg sys_rst_n; //active low

- initial

- begin

- sys_rst_n = 1'b0;

- #200;

- sys_rst_n = 1'b1;

- end

- wire led1,led2;

- LED_shining LED_shining_uut

- (

- .clk_in(sys_clk), //clk_in = 25mhz

- .rst_n_in(sys_rst_n), //rst_n_in, active low

- .led1(led1), //led1 output

- .led2(led2) //led2 output, opposite with led1

- );

- endmodule

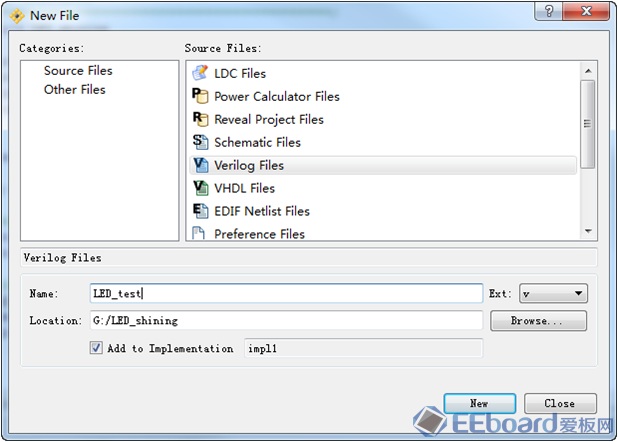

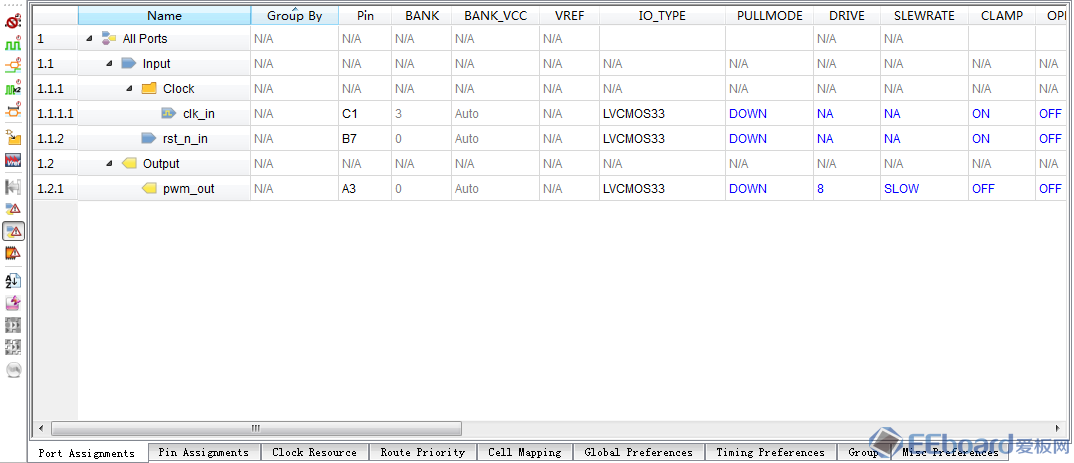

然后在软件左侧Process栏,选择File List,找到LED_test.v,右键选择Include for →Simulation

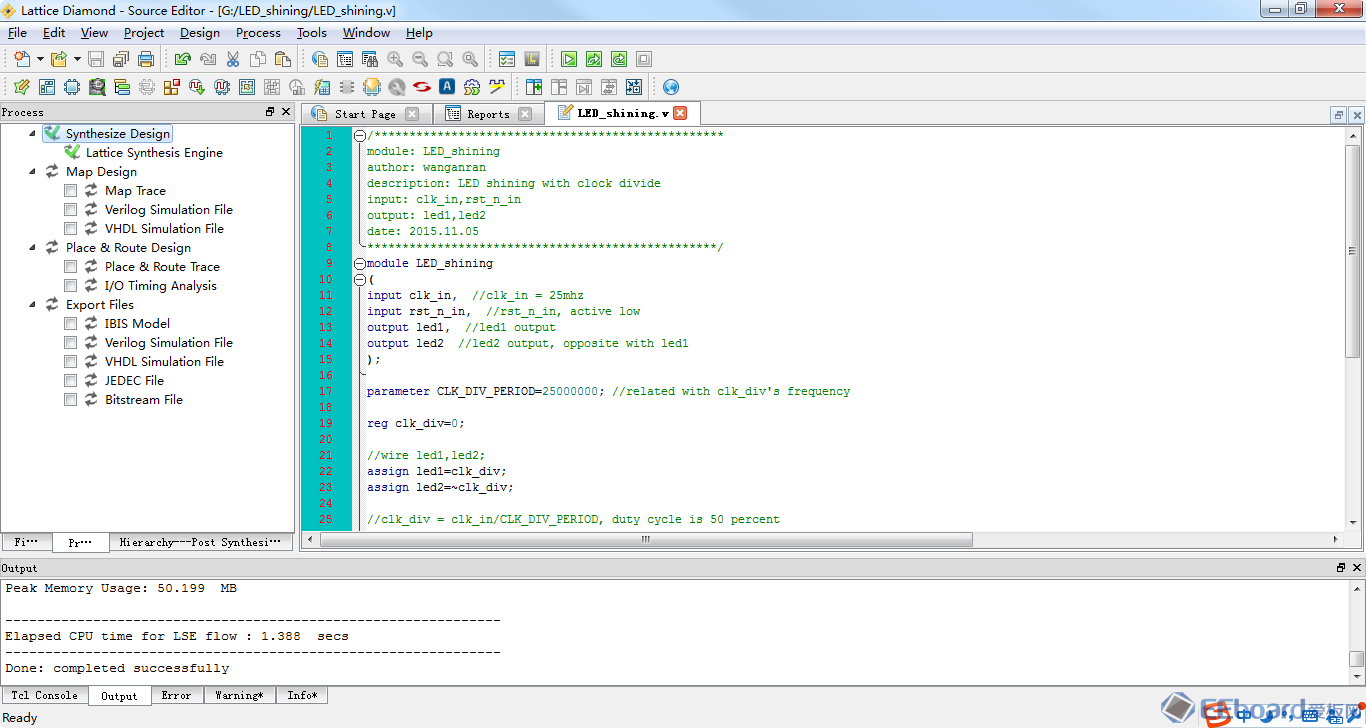

为了方便仿真,我们将LED_shining.v文件中的时钟分频周期缩短,更改并保存

parameter CLK_DIV_PERIOD=50;//25000000;//related with clk_div's frequency

仿真结束,编译下载时再恢复。

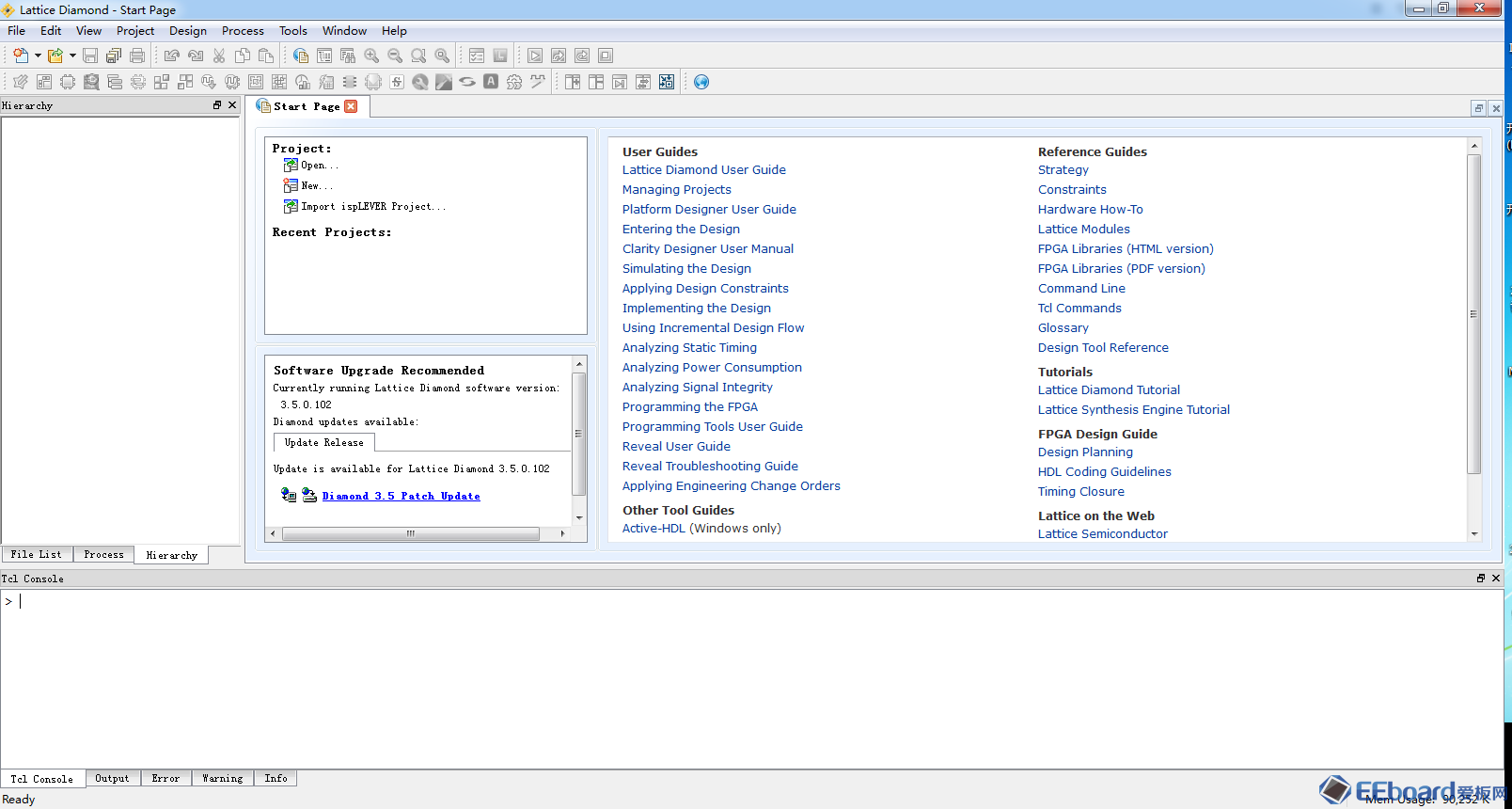

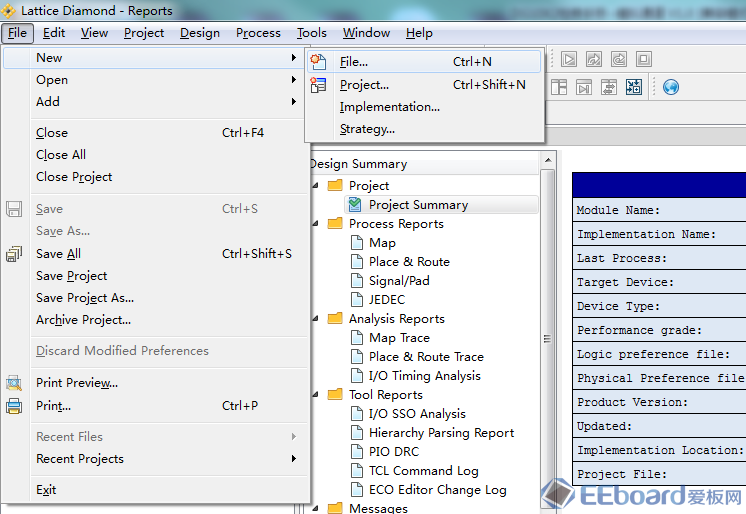

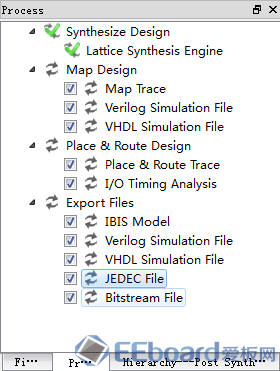

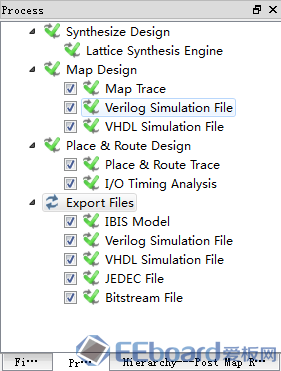

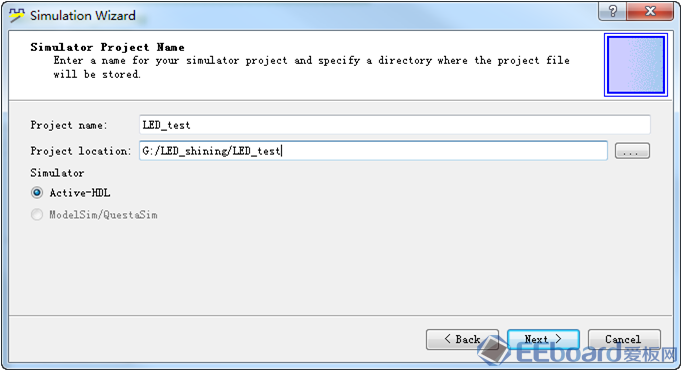

重新编译整个工程,然后选择Tools →SimulationWizard →Next,

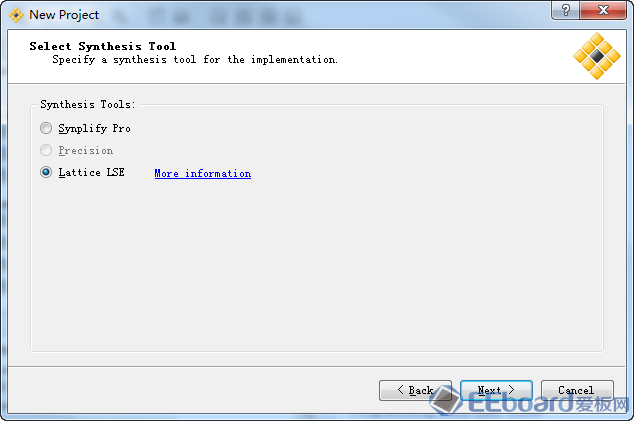

建立仿真工程,ModelSim和QuestaSim需要自行安装并与Diamond关联,才能直接调用,我们使用Active-HDL

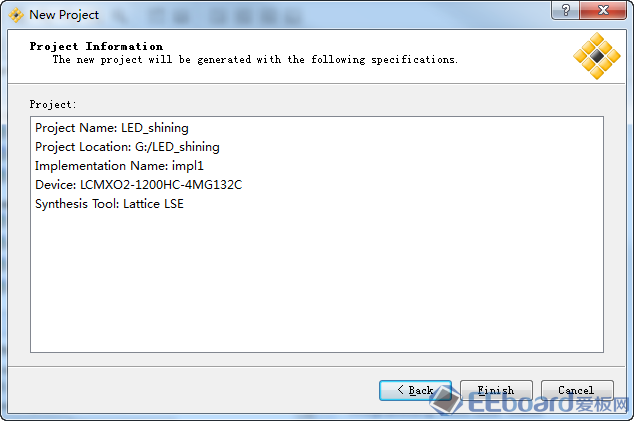

这里我们选择Active-HDL(默认),工程名称:LED_test,工程路径在Diamond工程路径下新建LED_test 文件夹:**/LED_shining/LED_test,然后Next,

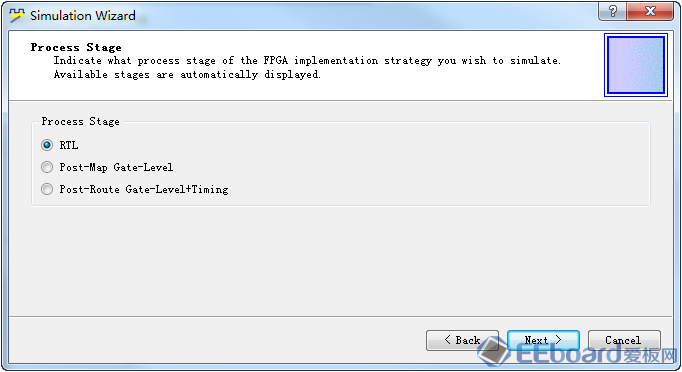

RTL,Next

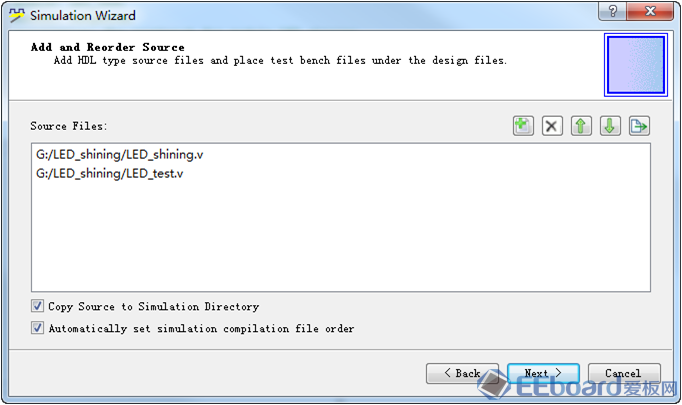

勾选Copy Source toSimulation Directory,Next

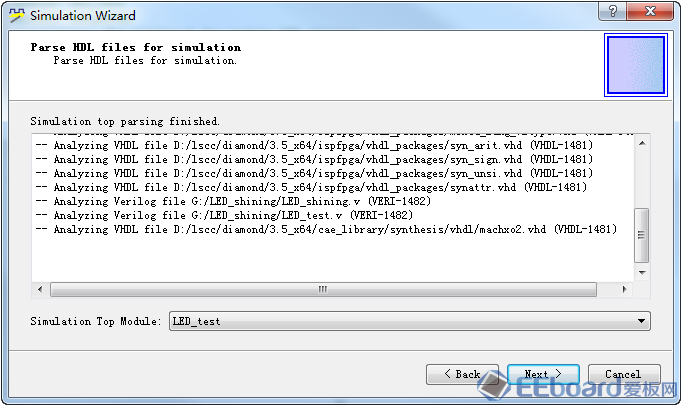

Next

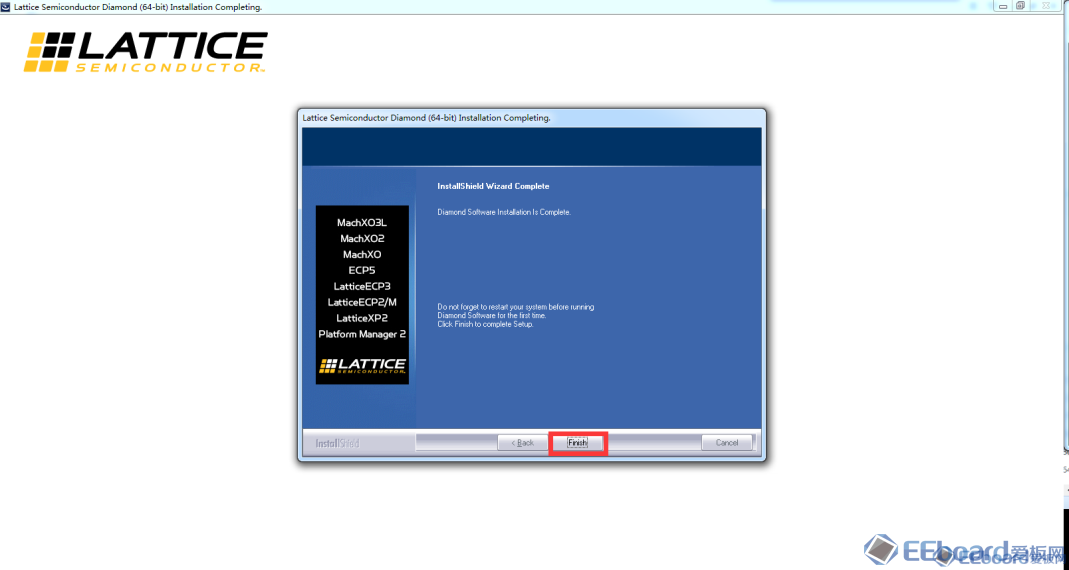

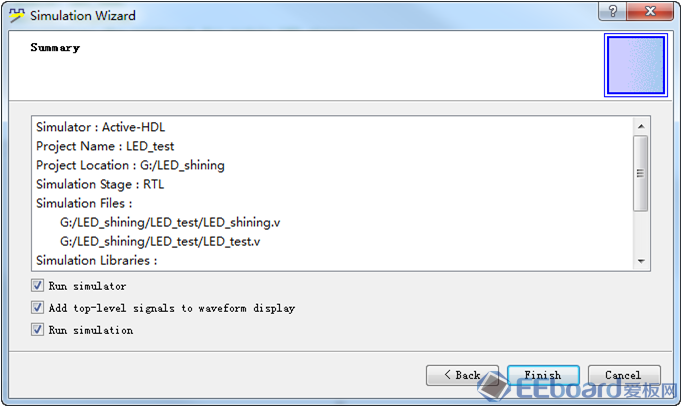

Finish

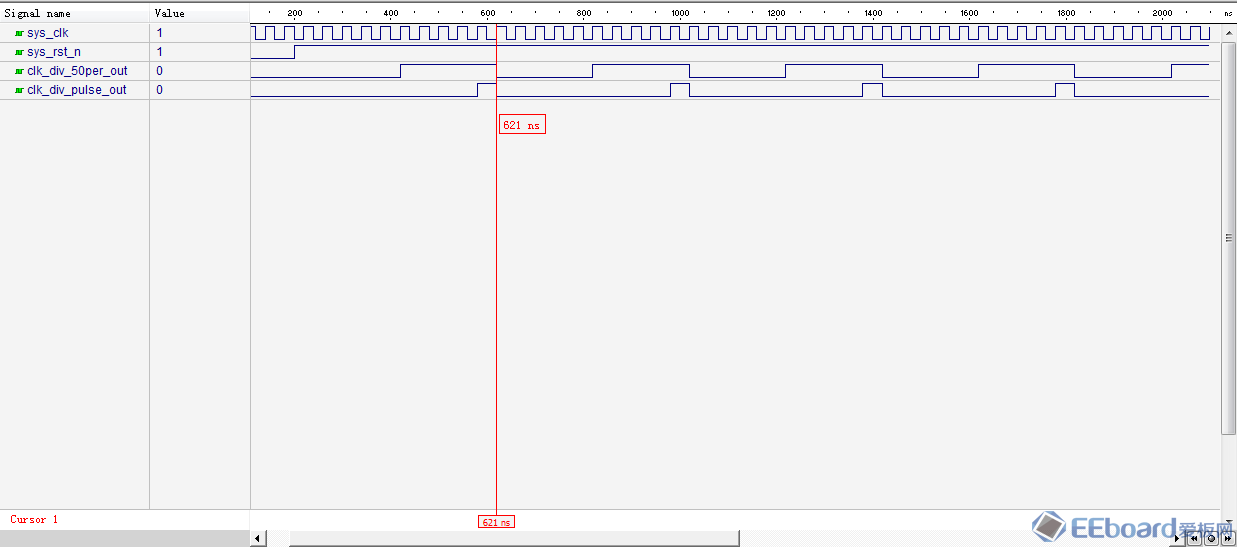

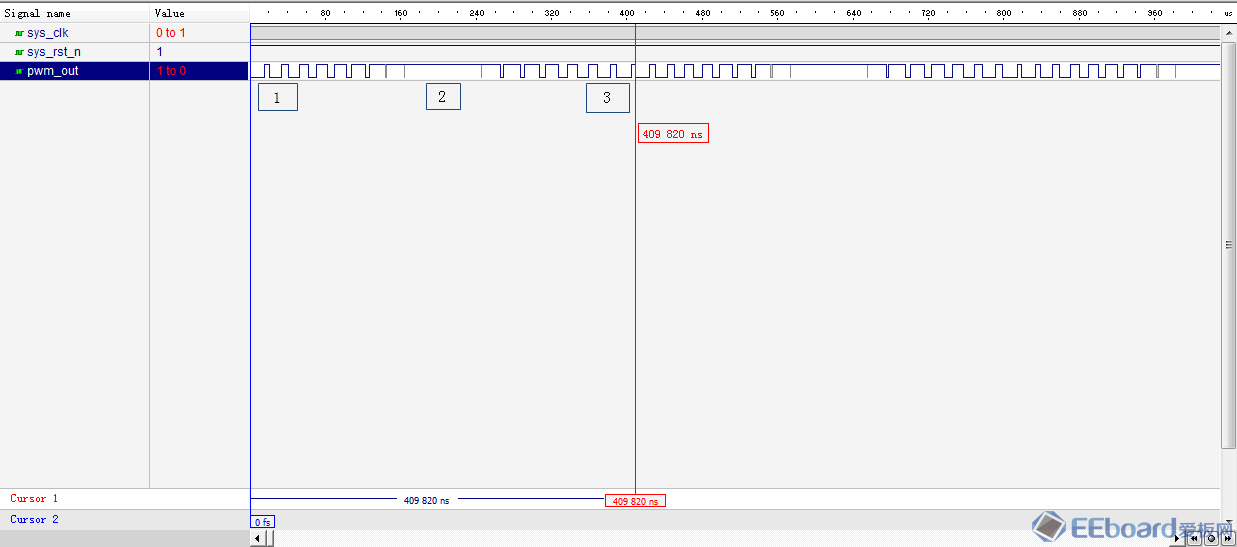

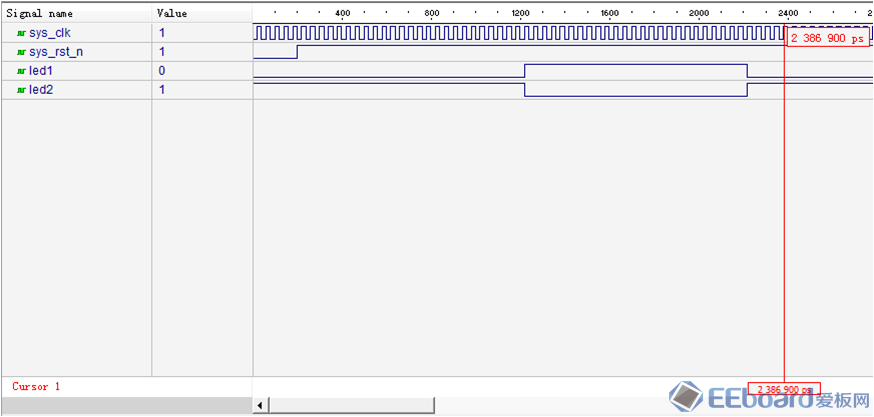

等待=====Active-HDL软件自动运行并显示仿真时序,查看仿真结果。

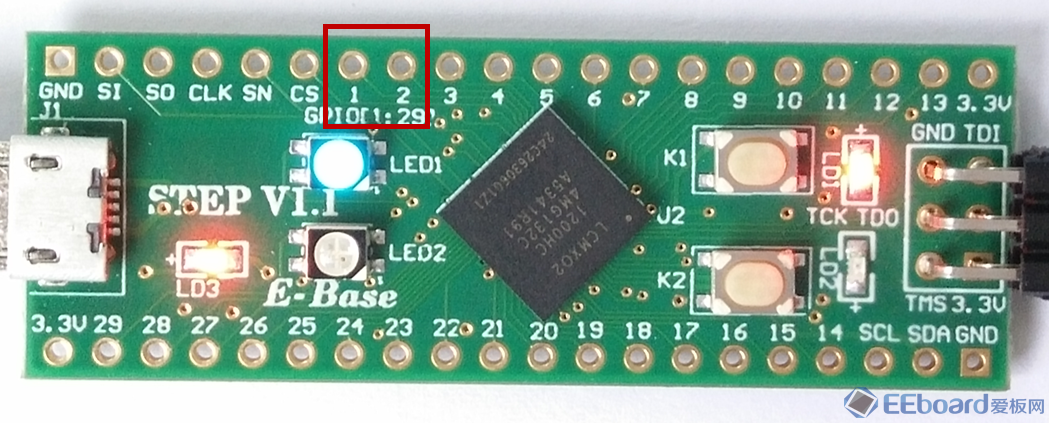

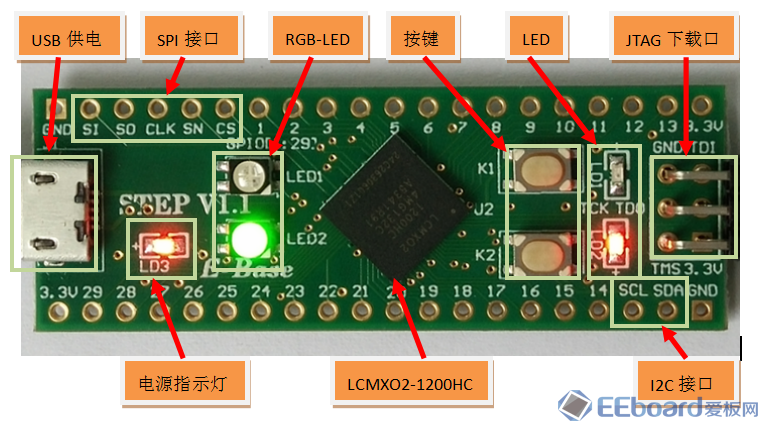

step fpga starter kit_board.pdf (61.55 KB, 下载次数: 21)

step fpga starter kit_board.pdf (61.55 KB, 下载次数: 21)